# DECADE COUNTER; DIVIDE-BY-TWELVE COUNTER; 4-BIT BINARY COUNTER

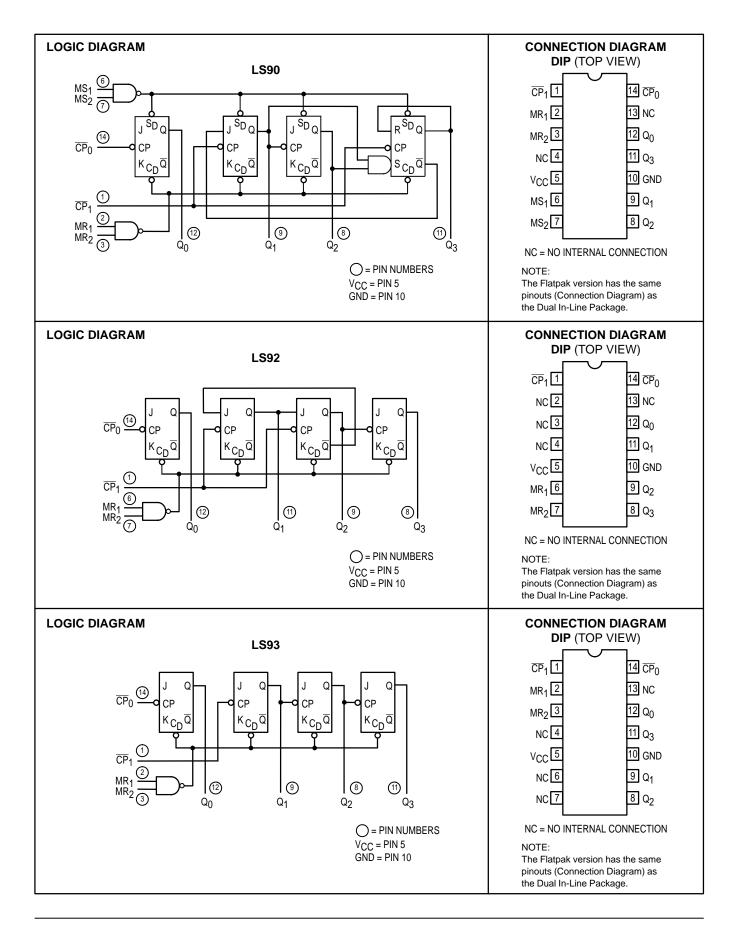

The SN54/74LS90, SN54/74LS92 and SN54/74LS93 are high-speed 4-bit ripple type counters partitioned into two sections. Each counter has a divide-by-two section and either a divide-by-five (LS90), divide-by-six (LS92) or divide-by-eight (LS93) section which are triggered by a HIGH-to-LOW transition on the clock inputs. Each section can be used separately or tied together (Q to  $\overline{CP}$ ) to form BCD, bi-quinary, modulo-12, or modulo-16 counters. All of the counters have a 2-input gated Master Reset (Clear), and the LS90 also has a 2-input gated Master Set (Preset 9).

- Low Power Consumption . . . Typically 45 mW

- High Count Rates . . . Typically 42 MHz

- Choice of Counting Modes . . . BCD, Bi-Quinary, Divide-by-Twelve, Binary

- Input Clamp Diodes Limit High Speed Termination Effects

| PIN NAMES                         |                                                                                | LOADIN   | G (Note a)   |

|-----------------------------------|--------------------------------------------------------------------------------|----------|--------------|

|                                   |                                                                                | HIGH     | LOW          |

| CP <sub>0</sub>                   | Clock (Active LOW going edge) Input to<br>÷2 Section                           | 0.5 U.L. | 1.5 U.L.     |

| CP <sub>1</sub>                   | Clock (Active LOW going edge) Input to<br>÷5 Section (LS90), ÷6 Section (LS92) | 0.5 U.L. | 2.0 U.L.     |

| CP <sub>1</sub>                   | Clock (Active LOW going edge) Input to<br>+8 Section (LS93)                    | 0.5 U.L. | 1.0 U.L.     |

| $MR_1, MR_2$                      | Master Reset (Clear) Inputs                                                    | 0.5 U.L. | 0.25 U.L.    |

| MS <sub>1</sub> , MS <sub>2</sub> | Master Set (Preset-9, LS90) Inputs                                             | 0.5 U.L. | 0.25 U.L.    |

| Q <sub>0</sub>                    | Output from +2 Section (Notes b & c)                                           | 10 U.L.  | 5 (2.5) U.L. |

| $Q_1, Q_2, Q_3$                   | Outputs from ÷5 (LS90), ÷6 (LS92),<br>÷8 (LS93) Sections (Note b)              | 10 U.L.  | 5 (2.5) U.L. |

NOTES:

a. 1 TTL Unit Load (U.L.) = 40  $\mu A$  HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military, (54) and 5 U.L. for commercial (74) Temperature Ranges.

c. The Q<sub>0</sub> Outputs are guaranteed to drive the full fan-out plus the CP<sub>1</sub> input of the device.

d. To insure proper operation the rise  $(t_r)$  and fall time  $(t_f)$  of the clock must be less than 100 ns.

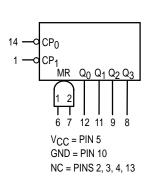

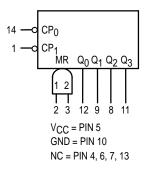

# LS90 6 7 1 2 $14 - CP_0$ $1 - CP_1$ $MR Q_0 Q_1 Q_2 Q_3$ 1 2 2 3 12 9 8 11 $V_{CC} = PIN 5$ GND = PIN 10NC = PIN 5 4, 13

# SN54/74LS90 SN54/74LS92 SN54/74LS93

### DECADE COUNTER; DIVIDE-BY-TWELVE COUNTER; 4-BIT BINARY COUNTER

LOW POWER SCHOTTKY

## LOGIC SYMBOL

LS92

LS93

FAST AND LS TTL DATA

### FUNCTIONAL DESCRIPTION

The LS90, LS92, and LS93 are 4-bit ripple type Decade, Divide-By-Twelve, and Binary Counters respectively. Each device consists of four master/slave flip-flops which are internally connected to provide a divide-by-two section and a divide-by-five (LS90), divide-by-six (LS92), or divide-by-eight (LS93) section. Each section has a separate clock input which initiates state changes of the counter on the HIGH-to-LOW clock transition. State changes of the Q outputs do not occur simultaneously because of internal ripple delays. Therefore, decoded output signals are subject to decoding spikes and should not be used for clocks or strobes. The Q<sub>0</sub> output of each device is designed and specified to drive the rated fan-out plus the  $\overline{CP}_1$  input of the device.

A gated AND asynchronous Master Reset (MR<sub>1</sub> • MR<sub>2</sub>) is provided on all counters which overrides and clocks and resets (clears) all the flip-flops. A gated AND asynchronous Master Set (MS<sub>1</sub> • MS<sub>2</sub>) is provided on the LS90 which overrides the clocks and the MR inputs and sets the outputs to nine (HLLH).

Since the output from the divide-by-two section is not internally connected to the succeeding stages, the devices may be operated in various counting modes.

#### LS90

- A. BCD Decade (8421) Counter The  $\overline{CP}_1$  input must be externally connected to the  $Q_0$  output. The  $\overline{CP}_0$  input receives the incoming count and a BCD count sequence is produced.

- B. Symmetrical Bi-quinary Divide-By-Ten Counter The Q<sub>3</sub> output must be externally connected to the  $\overline{CP}_0$  input. The input count is then applied to the  $\overline{CP}_1$  input and a divide-by-ten square wave is obtained at output Q<sub>0</sub>.

C. Divide-By-Two and Divide-By-Five Counter — No external interconnections are required. The first flip-flop is used as a binary element for the divide-by-two function ( $\overline{CP}_0$  as the input and  $Q_0$  as the output). The  $\overline{CP}_1$  input is used to obtain binary divide-by-five operation at the  $Q_3$  output.

### LS92

- A. Modulo 12, Divide-By-Twelve Counter The  $\overline{CP}_1$  input must be externally connected to the Q<sub>0</sub> output. The  $\overline{CP}_0$  input receives the incoming count and Q<sub>3</sub> produces a symmetrical divide-by-twelve square wave output.

- B. Divide-By-Two and Divide-By-Six Counter —No external interconnections are required. The first flip-flop is used as a binary element for the divide-by-two function. The  $\overline{CP}_1$  input is used to obtain divide-by-three operation at the  $Q_1$  and  $Q_2$  outputs and divide-by-six operation at the  $Q_3$  output.

### LS93

- A. 4-Bit Ripple Counter The output  $Q_0$  must be externally connected to input  $\overline{CP}_1$ . The input count pulses are applied to input  $\overline{CP}_0$ . Simultaneous divisions of 2, 4, 8, and 16 are performed at the  $Q_0$ ,  $Q_1$ ,  $Q_2$ , and  $Q_3$  outputs as shown in the truth table.

- B. 3-Bit Ripple Counter— The input count pulses are applied to input  $\overline{CP}_1$ . Simultaneous frequency divisions of 2, 4, and 8 are available at the  $Q_1$ ,  $Q_2$ , and  $Q_3$  outputs. Independent use of the first flip-flop is available if the reset function coincides with reset of the 3-bit ripple-through counter.

#### LS90 MODE SELECTION

| RES             | RESET/SET INPUTS |                 |                 |  |                | UTP | UTS |   |  |  |  |

|-----------------|------------------|-----------------|-----------------|--|----------------|-----|-----|---|--|--|--|

| MR <sub>1</sub> | MR <sub>2</sub>  | MS <sub>1</sub> | MS <sub>2</sub> |  | Q <sub>0</sub> | Q3  |     |   |  |  |  |

| н               | Н                | L               | Х               |  | L              | L   | L   | Г |  |  |  |

| н               | н                | Х               | L               |  | L              | L   | L   | L |  |  |  |

| X               | X                | н               | н               |  | н              | L   | L   | Н |  |  |  |

| L               | X                | L               | Х               |  |                | Cou | unt |   |  |  |  |

| X               | L                | Х               | L               |  |                | Οοι | Int |   |  |  |  |

| L               | X                | Х               | L               |  | Count          |     |     |   |  |  |  |

| Х               | L                | L               | Х               |  |                | Соι | unt |   |  |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

#### LS92 AND LS93 MODE SELECTION

|                 | SET<br>UTS      |                | OUTF                                         | PUTS |   |  |  |  |  |

|-----------------|-----------------|----------------|----------------------------------------------|------|---|--|--|--|--|

| MR <sub>1</sub> | MR <sub>2</sub> | Q <sub>0</sub> | Q <sub>0</sub> Q <sub>1</sub> Q <sub>2</sub> |      |   |  |  |  |  |

| Н               | Н               | L              | L                                            | L    | Г |  |  |  |  |

| L               | н               |                | Со                                           | unt  |   |  |  |  |  |

| Н               | L               | Count          |                                              |      |   |  |  |  |  |

| L               | L               |                | Со                                           | unt  |   |  |  |  |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

| LS90               |  |  |  |  |  |  |  |  |  |  |

|--------------------|--|--|--|--|--|--|--|--|--|--|

| BCD COUNT SEQUENCE |  |  |  |  |  |  |  |  |  |  |

| COUNT |                | OUT            | PUT |    |

|-------|----------------|----------------|-----|----|

| COUNT | Q <sub>0</sub> | Q <sub>1</sub> | Q2  | Q3 |

| 0     | L              | L              | L   | L  |

| 1     | Н              | L              | L   | L  |

| 2     | L              | Н              | L   | L  |

| 3     | Н              | Н              | L   | L  |

| 4     | L              | L              | Н   | L  |

| 5     | Н              | L              | Н   | L  |

| 6     | L              | Н              | Н   | L  |

| 7     | Н              | Н              | Н   | L  |

| 8     | L              | L              | L   | Н  |

| 9     | н              | L              | L   | Н  |

<u>NO</u>TE: Output  $Q_0$  is connected to Input  $CP_1$  for BCD count.

#### LS92 TRUTH TABLE

| COUNT | OUTPUT         |                |    |    |  |  |  |  |

|-------|----------------|----------------|----|----|--|--|--|--|

| COUNT | Q <sub>0</sub> | Q <sub>1</sub> | Q2 | Q3 |  |  |  |  |

| 0     | L              | L              | L  | L  |  |  |  |  |

| 1     | н              | L              | L  | L  |  |  |  |  |

| 2     | L              | Н              | L  | L  |  |  |  |  |

| 3     | н              | Н              | L  | L  |  |  |  |  |

| 4     | L              | L              | Н  | L  |  |  |  |  |

| 5     | н              | L              | Н  | L  |  |  |  |  |

| 6     | L              | L              | L  | н  |  |  |  |  |

| 7     | н              | L              | L  | н  |  |  |  |  |

| 8     | L              | Н              | L  | н  |  |  |  |  |

| 9     | н              | Н              | L  | Н  |  |  |  |  |

| 10    | L              | L              | Н  | н  |  |  |  |  |

| 11    | н              | L              | Н  | Н  |  |  |  |  |

$\underline{\text{NOTE:}}$  Output  $\text{Q}_0$  is connected to Input  $\text{CP}_1.$

LS93 TRUTH TABLE

| COUNT  |                | OUT            | PUT |    |

|--------|----------------|----------------|-----|----|

| COUNT  | Q <sub>0</sub> | Q <sub>1</sub> | Q2  | Q3 |

| 0      | L              | L              | L   | Г  |

| 1      | н              | L              | L   | L  |

| 2<br>3 | L              | Н              | L   | L  |

| 3      | Н              | Н              | L   | L  |

| 4      | L              | L              | Н   |    |

| 5      | Н              | L              | Н   | L  |

| 6      | L              | Н              | Н   | L  |

| 7      | Н              | Н              | Н   | L  |

| 8      | L              | L              | L   | н  |

| 9      | Н              | L              | L   | н  |

| 10     | L              | Н              | L   | Н  |

| 11     | н              | Н              | L   | Н  |

| 12     | L              | L              | Н   | н  |

| 13     | Н              | L              | Н   | н  |

| 14     | L              | Н              | Н   | н  |

| 15     | н              | Н              | Н   | н  |

$\underline{\text{NOTE:}}$  Output  $\text{Q}_0$  is connected to Input  $\text{CP}_1.$

### **GUARANTEED OPERATING RANGES**

| Symbol          | Parameter                           |          | Min         | Тур        | Max         | Unit |

|-----------------|-------------------------------------|----------|-------------|------------|-------------|------|

| VCC             | Supply Voltage                      | 54<br>74 | 4.5<br>4.75 | 5.0<br>5.0 | 5.5<br>5.25 | V    |

| т <sub>А</sub>  | Operating Ambient Temperature Range | 54<br>74 | -55<br>0    | 25<br>25   | 125<br>70   | °C   |

| ЮН              | Output Current — High               | 54, 74   |             |            | -0.4        | mA   |

| I <sub>OL</sub> | Output Current — Low                | 54<br>74 |             |            | 4.0<br>8.0  | mA   |

### DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)

|                 |                                                                                                          |        |     | Limits |                              |      |                                                                                |                                                       |  |

|-----------------|----------------------------------------------------------------------------------------------------------|--------|-----|--------|------------------------------|------|--------------------------------------------------------------------------------|-------------------------------------------------------|--|

| Symbol          | Parameter                                                                                                |        | Min | Тур    | Max                          | Unit | Test Co                                                                        | onditions                                             |  |

| VIH             | Input HIGH Voltage                                                                                       |        | 2.0 |        |                              | V    | Guaranteed Input HIGH Voltage for<br>All Inputs                                |                                                       |  |

| \/              |                                                                                                          |        |     |        | 0.7                          | v    | Guaranteed Input                                                               | LOW Voltage for                                       |  |

| VIL             | Input LOW Voltage                                                                                        | 74     |     |        | 0.8                          | V    | All Inputs                                                                     |                                                       |  |

| VIK             | Input Clamp Diode Voltage                                                                                |        |     | -0.65  | -1.5                         | V    | V <sub>CC</sub> = MIN, I <sub>IN</sub> = -18 mA                                |                                                       |  |

| Mari            |                                                                                                          | 54     | 2.5 | 3.5    |                              | V    | V <sub>CC</sub> = MIN, I <sub>OH</sub> = MAX, V <sub>IN</sub> = V <sub>I</sub> |                                                       |  |

| ∨он             | Output HIGH Voltage                                                                                      | 74     | 2.7 | 3.5    |                              | V    | or VIL per Truth Ta                                                            | able                                                  |  |

| Ver             |                                                                                                          | 54, 74 |     | 0.25   | 0.4                          | V    | I <sub>OL</sub> = 4.0 mA                                                       | $V_{CC} = V_{CC} MIN,$<br>$V_{IN} = V_{IL} or V_{IH}$ |  |

| VOL             | Output LOW Voltage                                                                                       | 74     |     | 0.35   | 0.5                          | V    | I <sub>OL</sub> = 8.0 mA                                                       | per Truth Table                                       |  |

|                 |                                                                                                          |        |     |        | 20                           | μΑ   | $V_{CC} = MAX, V_{IN}$                                                         | = 2.7 V                                               |  |

| ін              | Input HIGH Current                                                                                       |        |     |        | 0.1                          | mA   | $V_{CC} = MAX, V_{IN}$                                                         | = 7.0 V                                               |  |

| Ι <sub>ΙL</sub> | Input LOW Current<br>MS, MR<br>CP <sub>0</sub><br>CP <sub>1</sub> (LS90, LS92)<br>CP <sub>1</sub> (LS93) |        |     |        | -0.4<br>-2.4<br>-3.2<br>-1.6 | mA   | $V_{CC} = MAX, V_{IN} = 0.4 V$                                                 |                                                       |  |

| IOS             | Short Circuit Current (Note 1)                                                                           |        | -20 |        | -100                         | mA   | V <sub>CC</sub> = MAX                                                          |                                                       |  |

| ICC             | Power Supply Current                                                                                     |        |     |        | 15                           | mA   | V <sub>CC</sub> = MAX                                                          |                                                       |  |

Note 1: Not more than one output should be shorted at a time, nor for more than 1 second.

|                                      |                                                            |     | Limits   |          |     |          |          |     |          |          |      |

|--------------------------------------|------------------------------------------------------------|-----|----------|----------|-----|----------|----------|-----|----------|----------|------|

|                                      |                                                            |     | LS90     |          |     | LS92     |          |     | LS93     |          |      |

| Symbol                               | Parameter                                                  | Min | Тур      | Max      | Min | Тур      | Max      | Min | Тур      | Max      | Unit |

| fMAX                                 | CP0 Input Clock Frequency                                  | 32  |          |          | 32  |          |          | 32  |          |          | MHz  |

| fMAX                                 | CP1 Input Clock Frequency                                  | 16  |          |          | 16  |          |          | 16  |          |          | MHz  |

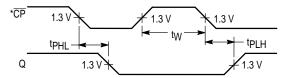

| <sup>t</sup> PLH<br><sup>t</sup> PHL | Propagation Delay, $\overline{CP}_0$ Input to $Q_0$ Output |     | 10<br>12 | 16<br>18 |     | 10<br>12 | 16<br>18 |     | 10<br>12 | 16<br>18 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | $\overline{CP}_0$ Input to Q <sub>3</sub> Output           |     | 32<br>34 | 48<br>50 |     | 32<br>34 | 48<br>50 |     | 46<br>46 | 70<br>70 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | $\overline{CP}_1$ Input to $Q_1$ Output                    |     | 10<br>14 | 16<br>21 |     | 10<br>14 | 16<br>21 |     | 10<br>14 | 16<br>21 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | $\overline{CP}_1$ Input to Q <sub>2</sub> Output           |     | 21<br>23 | 32<br>35 |     | 10<br>14 | 16<br>21 |     | 21<br>23 | 32<br>35 | ns   |

| <sup>t</sup> PLH<br><sup>t</sup> PHL | $\overline{CP}_1$ Input to Q <sub>3</sub> Output           |     | 21<br>23 | 32<br>35 |     | 21<br>23 | 32<br>35 |     | 34<br>34 | 51<br>51 | ns   |

| <sup>t</sup> PLH                     | MS Input to $Q_0$ and $Q_3$ Outputs                        |     | 20       | 30       |     |          |          |     |          |          | ns   |

| <sup>t</sup> PHL                     | MS Input to $Q_1$ and $Q_2$ Outputs                        |     | 26       | 40       |     |          |          |     |          |          | ns   |

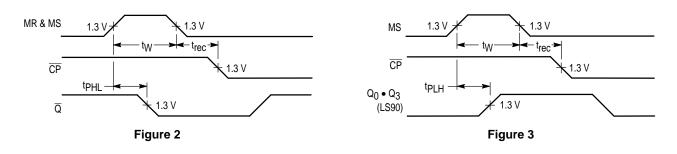

| <sup>t</sup> PHL                     | MR Input to Any Output                                     |     | 26       | 40       |     | 26       | 40       |     | 26       | 40       | ns   |

# AC CHARACTERISTICS (T\_A = 25°C, V\_{CC} = 5.0 V, C\_L = 15 pF)

AC SETUP REQUIREMENTS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                  |                             | Limits |     |      |     |      |     |      |

|------------------|-----------------------------|--------|-----|------|-----|------|-----|------|

|                  |                             | LS90   |     | LS92 |     | LS93 |     |      |

| Symbol           | Parameter                   | Min    | Мах | Min  | Max | Min  | Мах | Unit |

| tw               | CP <sub>0</sub> Pulse Width | 15     |     | 15   |     | 15   |     | ns   |

| t <sub>W</sub>   | CP <sub>1</sub> Pulse Width | 30     |     | 30   |     | 30   |     | ns   |

| tW               | MS Pulse Width              | 15     |     |      |     |      |     | ns   |

| t <sub>W</sub>   | MR Pulse Width              | 15     |     | 15   |     | 15   |     | ns   |

| t <sub>rec</sub> | Recovery Time MR to CP      | 25     |     | 25   |     | 25   |     | ns   |

RECOVERY TIME (trec) is defined as the minimum time required between the end of the reset pulse and the clock transition from HIGH-to-LOW in order to recognize and transfer HIGH data to the Q outputs

#### AC WAVEFORMS

#### Figure 1

\*The number of Clock Pulses required between the tPHL and tPLH measurements can be determined from the appropriate Truth Tables.

## FAST AND LS TTL DATA